摘要

让我们一起探索编码序列检验器的奥秘,用滑动窗口法和均值滤波,让FPGA在verilog的指引下,完成同步帧头的神奇旅程。让我们一起感受这份技术的魅力吧!

正文

通讯中人们常见编码序列探测器用于检验通讯帧的同歩帧头,为此做到同歩的目地。编码序列检验便是针对持续键入的二进制数据流分析中检查出特殊编码序列的二进制数据流分析。

例如在10101100100101中检验110010。这类一般选用移位寄存器来完成,能够自主百度搜索:移位寄存器完成编码序列检验。

关键词:滑动窗口法;verilog;FPGA;均值滤波

殊不知这篇博闻想传递的思维是:大家可不可以立即挪动检验取样后的数据流分析呢? 例如取样8bit din:8‘d55,8’d111,8’d40,8’d122,8’d100,8’d30,8’d120,大家想检验出8’d111,8’d40,8’d122,8’d100。

那样做会对信息开展均值滤波,这类观念还能够用于做扩频通信接受中的匹配滤波捕捉,文中就拿均值滤波来举个例子吧。

假定我们要在取样到的数据流分析开展均值滤波,数据流分析键入为12bit,一帧有6五个数据信息,对话框尺寸为5,对导入数据信息选用1/4平均值。

编码以下:

module data_capture ( input clk,rstn, input in_vld, input[11:0] din, output reg out_vld, output reg[31:0] dout ); parameter AVE_DATA_NUM = 3'd5; /////////////////////Shift register/////////////////////////// reg [11:0] data_reg [AVE_DATA_NUM-1:0]; reg [3:0]temp_i; always @ (posedge clk) begin if(rstn || !in_vld) for (temp_i=0; temp_i<AVE_DATA_NUM; temp_i=temp_i 1) data_reg[temp_i] <= 'd0; else begin data_reg[0] <= din; for (temp_i=0; temp_i<AVE_DATA_NUM-1; temp_i=temp_i 1) data_reg[temp_i 1] <= data_reg[temp_i]; end end /////////////////////sum////////////////////////////// reg [31:0] sum; always @ (posedge clk ) begin if (rstn || !in_vld) sum <= 'd0; else sum <= sum din - data_reg[AVE_DATA_NUM-1]; //Replace the oldest data with the latest input data end ////////////////////cnt//////////////////////////// reg[8:0] cnt; always @(posedge clk) begin if (rstn || !in_vld) cnt <= 'd0; else if(cnt == 9'd64) cnt <= 0; else cnt <= cnt 1'b1; end ///////////////////dout//////////////////////////// always @(posedge clk) begin if (rstn || !in_vld) begin dout <= 11'd0; out_vld <= 1'd0; end else if(cnt > 9'd4) begin out_vld <= 1'b1; dout <= sum>>2; //sum/4。 end else begin out_vld <= 1'b0; dout <= 0; end end endmodule

一帧64个12bit,由于对话框尺寸为5,仅有当第5个数据信息来临时才逐渐取平均值,与此同时拉升out_vld。

testbeach以下:

`timescale 1ns/1ns module capture_tb(); reg clk,rstn; reg in_vld; reg[11:0] din; wire out_vld; wire[31:0] dout; initial begin clk = 1; rstn = 1; in_vld = 0; #200 rstn = 0; in_vld = 1; #10000 $stop(); end always #10 clk = ~clk; always #20 din = {$random}%100; data_capture tb( .clk(clk),.rstn(rstn), .in_vld(in_vld), .din(din), .out_vld(out_vld), .dout(dout) ); endmodule

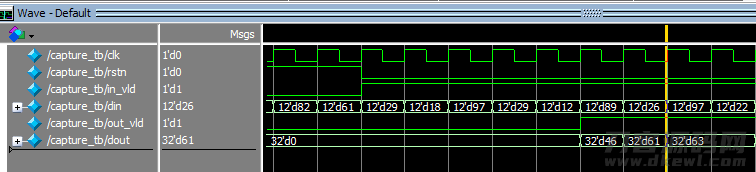

模拟仿真图以下所显示:

第一个dout为in_vld拉升以后的29,18,97,29,12的1/4平均值;

第二个dout为in_vld拉升后第二个clk逐渐取样获得的数据信息18,97,29,12,89的平均值,刚来的89把最早的29给顶离开了。

实际上测算有一些是有小数的,可是FPGA就是这样,小数都想下求整了。

关注不迷路

扫码下方二维码,关注宇凡盒子公众号,免费获取最新技术内幕!

评论0